- Объявления /

- Радиодетали и электронные компоненты /

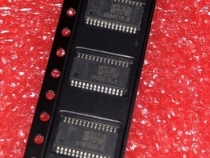

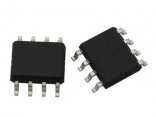

- Микросхема M24128-BWMN6TP, M24256-BWMN6TP, M24512-WMN6TP SOP-8 1 шт./лот

Микросхема M24128-BWMN6TP, M24256-BWMN6TP, M24512-WMN6TP SOP-8 1 шт./лот

ПРОДАЖАОписание

512 Kbit serial I²C bus EEPROM with three Chip Enable lines

Description

The M24512-x devices are I2C-compatible electrically erasable programmable memories

(EEPROM). They are organized as 64 Kb × 8 bits.

The M24512-D also offers an additional page, named the Identification Page (128 bytes)

which can be written and (later) permanently locked in Read-only mode. This Identification

Page offers flexibility in the application board production line, as it can be used to store

unique identification parameters and/or parameters specific to the production line.

The device behaves as a slave in the I2C protocol, with all memory operations synchronized

by the serial clock. Read and Write operations are initiated by a Start condition, generated

by the bus master. The Start condition is followed by a device select code and Read/Write

bit (RW) terminated by an acknowledge bit.

When writing data to the memory, the device inserts an acknowledge bit during the 9th bit

time, following the bus master’s 8-bit transmission. When data is read by the bus master, the

bus master acknowledges the receipt of the data byte in the same way. Data transfers are

terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

Features

Compatible with all I²C bus modes:

– 1 MHz Fast-mode Plus

– 400 kHz Fast mode

– 100 kHz Standard mode

Memory array:

– 512 Kb (64 Kbytes) of EEPROM

– Page size: 128 bytes

M24512- DR: additional Write lockable Page

(Identification page)

Noise suppression

– Schmitt trigger inputs

– Input noise filter

Write

– Byte Write within 5 ms

– Page Write within 5 ms

Random and Sequential Read modes

Write protect of the whole memory array

Single supply voltage:

– 1.8 V to 5.5 V

– 2.5 V to 5.5 V

Enhanced ESD/Latch-Up protection

More than 1 million Write cycles

More than 40-year data retention

Packages

– ECOPACK2® (RoHS compliant and

Halogen-free)

Комментарии

Чтобы комментировать — надо зарегистрироваться

Ждем ваши комментарии