- Объявления /

- Радиодетали и электронные компоненты /

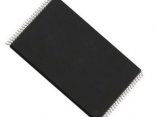

- Микросхема MT29F2G08AACWP TSOP48 NAND Flash Memory

Микросхема MT29F2G08AACWP TSOP48 NAND Flash Memory

ПРОДАЖАОписание

Features

• Organization

– Page size x8: 2,112 bytes (2,048 + 64 bytes)

– Page size x16: 1,056 words (1,024 + 32 words)

– Block size: 64 pages (128K + 4K bytes)

– Device size: 2Gb: 2,048 blocks; 4Gb: 4,096 blocks;

8Gb: 8,192 blocks

• READ performance

– Random READ: 25μs

– Sequential READ: 30ns (3V x8 only)

• WRITE performance

– PROGRAM PAGE: 300μs (TYP)

– BLOCK ERASE: 2ms (TYP)

• Endurance: 100,000 PROGRAM/ERASE cycles

• First block (block address 00h) guaranteed to be

valid without ECC (up to 1,000 PROGRAM/ERASE

cycles)

• VCC: 1.70V–1.95V1 or 2.7V–3.6V

• Automated PROGRAM and ERASE

• Basic NAND Flash command set:

– PAGE READ, READ for INTERNAL DATA MOVE,

RANDOM DATA READ, READ ID, READ STATUS,

PROGRAM PAGE, RANDOM DATA INPUT, PROGRAM

PAGE CACHE MODE, PROGRAM for

INTERNAL DATA MOVE, BLOCK ERASE, RESET

• New commands:

– PAGE READ CACHE MODE

– One-time programmable (OTP), including:

OTP DATA PROGRAM, OTP DATA PROTECT,

OTP DATA READ

– READ UNIQUE ID (contact factory)

– READ ID2 (contact factory)

• Operation status byte provides a software method of

detecting:

– PROGRAM/ERASE operation completion

– PROGRAM/ERASE pass/fail condition

– Write-protect status

• READY/BUSY (R/B#) pin provides a hardware

method of detecting PROGRAM or ERASE cycle

completion

• WP# pin: hardware write protect

General Description

NAND Flash technology provides a cost-effective solution for applications requiring

high-density, solid-state storage. Micron MT29F2G08AxC and MT29F2G16AxC devices

are 2Gb NAND Flash memory devices. The MT29F4G08BxC and MT29F4G16BxC are

4Gb devices. The MT29F8G08FAC is a four-die stack that operates as two independent

4Gb devices, providing a total storage capacity of 8Gb in a single, space-saving package.

These devices include standard NAND Flash features as well as new features designed to

enhance system-level performance.

Micron NAND Flash devices use a highly multiplexed 8- or 16-bit bus (I/O[7:0] or

I/O[15:0]) to transfer data, addresses, and instructions. The five command pins (CLE,

ALE, CE#, RE#, WE#) implement the NAND Flash command bus interface protocol. Two

additional pins control hardware write protection (WP#) and monitor device status

(R/B#).

This hardware interface creates a low-pin-count device with a standard pinout that is

the same from one density to another, supporting future upgrades to higher densities

without board redesign.

The MT29F2G and MT29F4G devices contain 2,048 and 4,096 erasable blocks, respectively.

Each block is subdivided into 64 programmable pages. Each page consists of

2,112 bytes (x8) or 1,056 words (x16). The pages are further divided into a 2,048-byte data

storage region with a separate 64-byte area on the x8 device; and on the x16 device, separate

1,024-word and 32-word areas. The 64-byte and 32-word areas are typically used

for error management functions.

The contents of each 2,112-byte page can be programmed in 300μs, and an entire 132Kbyte/

66K-word block can be erased in 2ms. On-chip control logic automates PROGRAM

and ERASE operations to maximize cycle endurance. ERASE/PROGRAM endurance is

specified at 100,000 cycles when appropriate error correction code (ECC) and error

Комментарии

Чтобы комментировать — надо зарегистрироваться

Ждем ваши комментарии